PCI-Express has been the standard for PC device connection for quite a while now. It’s primarily used to connect graphics cards as well as solid-state drivers to the motherboard. Lately, developers introduced the new PCI-Express 6.0 specification chart. In this guide we explore and explain the improvements and innovations of the sixth generation of the PCIe port.

The name PCI-Express 6.0 refers to the sixth generation of the interface and it includes several modifications with the fifth previous iterations of the technology. Each new generation introduces improvements and the higher performance is always the one we take into account the most. However, there are numerous characteristics to consider.

What is PCI-Express?

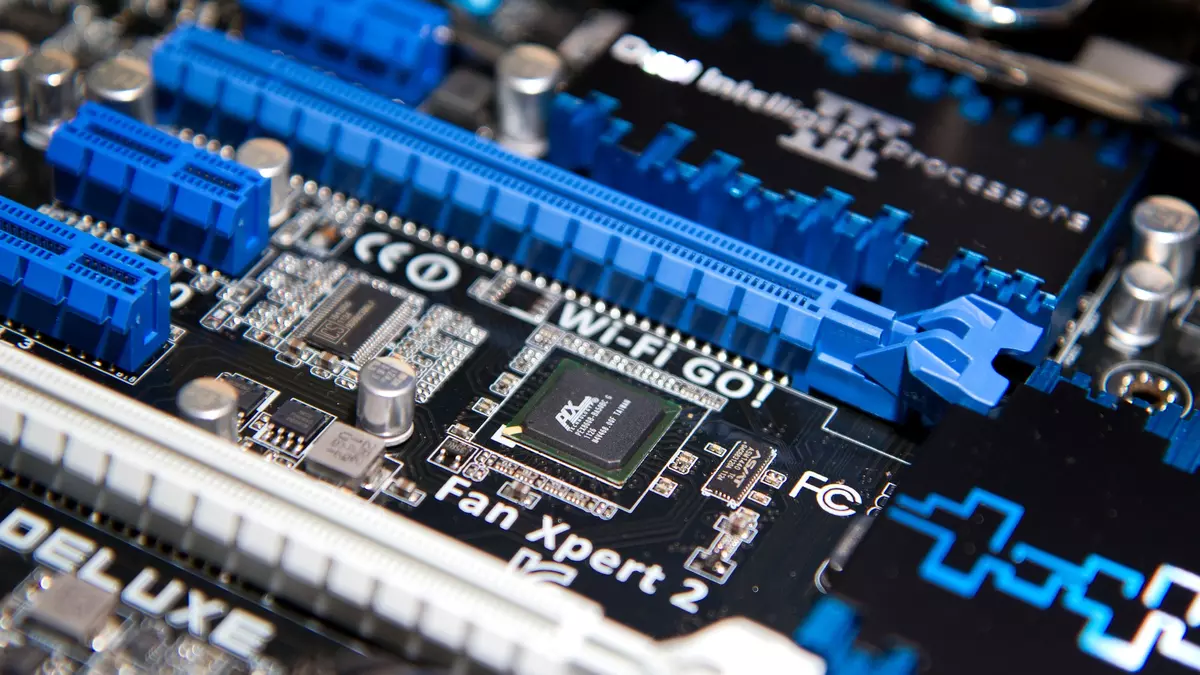

The name PCI Express stands for Peripheral Component Interconnect Express. This allows for a quick and easy connection of several devices to the motherboard. In order to understand the term well we can clarify two important elements:

- Peripherals: in a PC the peripheral is not only a keyboard, mouse or headphones. When talking about hardware the peripherals also include any device that can connect and disconnect from the computer such as graphics card, SSD or audio cards. Lots of peripherals use the PCI-Express interface standard.

- Interconnection: the use of this term instead of connection implies a bidirectional communication between two points. It’s not a one-way data transfer such as a graphics card sending data to the monitor, but both devices communicate with each other.

The PCI-Express standard is the interconnection interface that PCI-SIG developed. It’s a consortium of manufacturers and designers that agree on certain interface requirements to ensure that the devices can work together and communicate easily. The PCI-Express has been around since 2003. It originally started as an evolution of AGP and PCI standards. The PCIe 1.0 version appeared in 2003 and it was a very simple but representative: it could transfer data at 2.5 GT/s /GigaTransfers per second) and 250 MB/s per data lane.

The current PCIe 5.0 can handle 32 GT/s and 3,938 MB7s per data lane, an evident improvement that will go even further with the newest 6.0 version.

Technical specifications of the PCI-Express 6.0

Each new generation of the PCie interface means improvement. The 6.0 version offers double the bandwidth of PCIe 5.0 with 1, 4, 8 and 16 lanes sending data in parallel. This results in a data flow of up to 256 GB/s. It’s important to note that we talk about combined bandwidth in both directions reading and writing.

The backward compatibility

A great feature of the PCI Express is the backward compatibility with previous protocol versions. You can connect a PCIe 1.0 card to the PCIe 6.0 slot with no problems. The backward compatibility is possible thanks to the pin layout that has remained unchanged across all the interface versions.

Although the backward compatibility can be a double-edged sword. In order to increase the bandwidth, you can’t add additional pins and the interface’s clock speed must be risen. As a result, data transmission occurs at higher speeds for higher throughput and it leads to potential issues like high power consumption and heat generation.

The problems with PCI-Express 6.0

When you increase the clock speed of an interface it becomes more prone to stability issues. After six generations some changes allow PCIe to handle high speeds more comfortably. Transmitting 256 GB/s in a Full Duplex interface requires the interface speed to go up to 128 GHz with a significant compromise for signal integrity. To solve this issue, certain measures adopted like the new coding method called PAM4.

How does PAM4 work in PCI-Express 6.0

Depending on the voltage at which information travels the interface knows if the value transmitted is 1 or 0 (remember the elements work in a binary system). The binary systems use two voltage levels with enough separation to avoid signal confusion during voltage transitions.

The PCI-Express 6.0 solves the problem with Pulse Amplitude Modulation 4 coding (PAM4) the same one that GDDR6X memories use. This coding relies on four different voltage levels for each pin, allowing the encoding of the values 00, 01, 10 and 11. Finally, through this coding they avoid the need to increase bandwidth and pins but also hint that PCIe 7.0 may not be possible through conventional methods. The future versions may employ optical or photonic interfaces with several improvements in comparison with the newly PCIe 6.0. The waiting for the successor will require some patience.

Communication on PCI-Express 6.0 is not the same

The change to PAM4 coding has also transformed the way PCIe 6.0 sends its packets. It is still compatible with previous generations that used PAM2 or NRz system. But PAM4 does not support the previous packet system and there have been changes in the communication protocol.

The need for higher speed of PCIe 6.0 may cause instability and result in errors. Therefore, a new Forward Error Correction (FEC) protocol appeared. The new interface uses a type of package called FLIT that it’s a set of bits with a specific destination. The latency of each FLIT depends on the number of interface lanes, each packet having a latency of 2ns in a 16-lane PCIe 6.0 interface but up to 32 ns in single-lane interfaces.

FEC only works with fixed sizes, so the FLIT is set at 256 bytes per transmission. Each package or Transaction Layer Packet (TLP) has a size ranging from 0 bytes to 4096 bytes, meaning that a packet can consist of multiple FLITS.

And then we have the Cyclic Redundancy Check (CRC). It’s a system for error correction in the code that is commonly used in storage units and digital networks. Thhe CRC is integrated into the PCI-Express 6.0 standard for the verification of data transmitted from end to end. The objective is to maintain its integrity, ensuring that not a single bit is altered in the process..

The interface has specialized units that perform a series of polynomial calculations to keep the interface integrity. The feature is very important because there’s an enormous amount of data transmitted and you can save them with less leaks. It’s also an important addition for future SSD manufacturers that won’t need to add the feature to their devices as its comes into the interface.

Low-Power Mode in PCI-Express 6.0

On the other hand, PCIe 6.0 introduces a new low-power state called LOP. It allows the interface to reduce the power consumption when data flows below the maximum capacity. It can adjust the clock speed needed for each connected device during specific moments, when the data to be transmitted is at a lower volume.

Thanks to this mechanism and the new technologies PCIe 6.0 introduces, only new devices can make the most out of the new interface generation. However, older devices will also take advantage of general improvements PCIe introduces in the new generation. The Low Power Mode won’t have backward compatibility but the rest of the features are available.